Product Summary

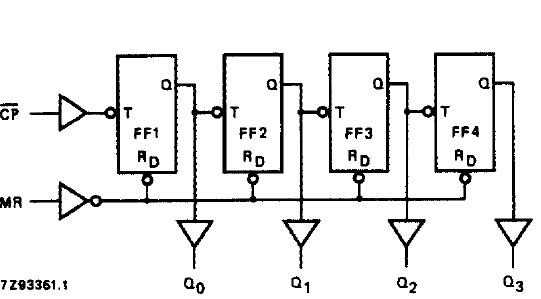

The 74HC32DR is a Dual 4-bit binary ripple counter and is pin compatible with low power Schottky TTL (LSTTL). The 74HC32DR is specified in compliance with JEDEC standard no. 7A. The 74HC32DR is a 4-bit binary ripple counter with separate clocks (1CP and 2 CP) and master reset (1MR and 2MR) inputs to each counter. The operation of each half of the “393” is the same as the “93” except no external clock connections are required.

Parametrics

74HC32DR absolute maximum ratings: (1)tPHL/ tPLH, propagation delay CL = 15 pF; VCC = 5 V, nCP to nQ0: 12ns; nQ to nQn+1: 5ns; nMR to nQn: 11ns; (2)fmax, maximum clock frequency: 99MHz; (3)CI, input capacitance: 3.5pF; (4)CPD, power dissipation capacitance per counter: 23pF.

Features

74HC32DR features: (1)Two 4-bit binary counters with individual clocks; (2)Divide-by any binary module up to 28 in one package; (3)Two master resets to clear each 4-bit counter individually; (4)Output capability: standard; (5)ICC category: MSI.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

74HC32DR2G |

|

IC GATE OR QUAD 2INPUT 14-SOIC |

Data Sheet |

|

|

||||||||||||||||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||||||||

|

74HC |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||||||||

|

74HC/HCT02 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||||||||

|

74HC/HCT03 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||||||||

|

74HC/HCT10 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||||||||

|

74HC/HCT107 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||||||||

|

74HC/HCT109 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||||||||

(Hong Kong)

(Hong Kong)